|

HSMC Quad Video Board |

| |

Features

- Four Separate Video Decoder

Channels

- Accepts NTSC (M, 4.43), PAL (B, D,

G, H, I, M, N), and SECAM (B, D, G, K, K1, L)

- Support ITU-R BT.601

- High-Speed 9-Bit ADC on each

channel

- Two Composite Inputs or One S-video

Input (for Each Channel)

- Total of 8 independent composite

input streams.

- Brightness, Contrast, Saturation,

Hue, and Sharpness Control Through i2c

- Four Independent Polymorphic

Scalers

- Standard Programmable Video Input

Format

- ITU-R BT.656, 8-Bit 4:2:2 With

Embedded/Discrete Syncs

- DVI Transmitter up to 165M

pixels/second (1600x1200, 1080p, etc)

- TV output supporting graphics

resolutions up to 1024 x768 pixels

- Support for all NTSC and PAL

formats on video output

- Provides CVBS, S-Video and SCART (RGB)

outputs

|

|

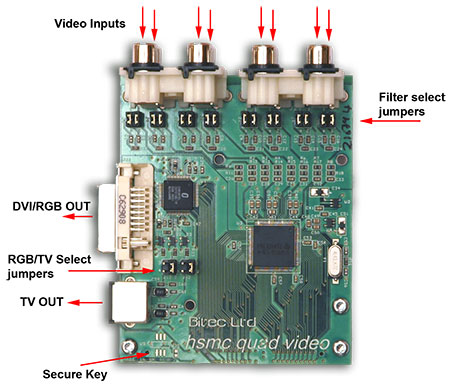

The hsmc quad video board is based on the

Texas Instruments TVP5154 quad video decoder. The analogue

video inputs supported by the TVP5154 include composite

video and S-video. In general, the video decoder converts

the analogue video input signal into digital component data.

This data and the associated clocks from the video decoder

are sent to the host fpga via the hsmc connector. A

pre-scalar is integrated into the device which allows

real-time scaling of input video data. The device is

controlled using i2c from the fpga.

Video output is based on the Chrontel

CH7010B

device. This device enables single-link DVI, component

analogue and composite analogue video outputs. The device

accepts digital, parallel video data and clocking from the

host fpga via the hsmc connector. The host fpga is able to

configure and monitor the device over an i2c link. A DVI

output connector and mini-din output connector is present on

the board.

The hsmc quad video daughter card also supports a serial

eeprom for FPGA design security. Developers can distribute

demonstrations of their IP locked to the hsmc bvdc card.

Datasheet下載 |

|

|