|

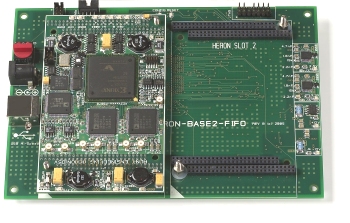

RTG001

- USB

主板連接1.5百萬FPGA

system,資料擷取與信號處理(包含高速的A/D和D/A) |

|

- User programmable Xilinx

XC2V1500-6 FPGA.

- 2 channels of 210Mhz 12

bit A/D

- 2 single ended

(optionally differential) channels of 160Mhz 16 bit D/A

- 8 bits digital I/O

- Hi Speed (480Mbits/sec)

USB 2.0 connection to a host PC.

- Can be used as a stand

alone board for embedded systems.

- FPGA can be configured

via USB, Xilinx JTAG cable or from on-board PROM

- Single 5V power supply

required ?20W mains Power Supply Unit included

Host API supported for Windows 2000 and XP and Linux

FPGA and DSP loading, resetting and data exchange all

performed with simple to use software interface.

- Optional expansion via

HERON module slot

|

| |

|

| |

The fast A/D and D/A channels

are directly connected to the user programmable FPGA,

allowing data to be processed by a user FPGA program. The

FPGA can be used to perform digital processing between the

analogue inputs and outputs, or the data can be passed to

and from a PC using the USB 2.0 connection and provided

software.

The USB connection is supported via the Host-API software.

This allows software applications and tools on the Host PC

to access the hardware using a consistent software interface

without the need to understand or program the hardware or

USB directly.

The FPGA program can be loaded over the USB connection using

a software tool that directly accepts the output from

development tools for the Xilinx FPGA. Alternatively a

Xilinx JTAG cable (Parallel or USB) can be used to load the

FPGA and or program the on board configuration PROM.

The FIFO connections can be used to stream data to or from a

module in the system. They are capable of up to

50Mbytes/second in each direction, but the Host PC, its USB

controller and the operating system will all impose their

own limits to this speed.

The system is delivered ready to go with a power supply

(requires an IEC lead specific to your country), USB cable,

I/O cables and a CD with all of your documentation, software

tools and examples. The only other thing you need are

development tools for the Xilinx FPGA, for example Xilinx

Foundation ISE from

www.xilinx.com .

- Analogue I/P

2 differential input

channels with common or independent clocking set by

jumper

Standard Input characteristics:

+/-0.768mV differential inputs each on 2 MMT

co-axial connectors (U.FL if you choose the

differential output option)

A/C coupled 50R, signal B/W from 200Hz to 450Mhz

Zero input noise typically 3 levels maximum 8 levels

Offset typically +-3 levels maximum +-8 levels

Optional Input types:

D/C

D/C coupled 50R - Signal B/W 0hz to 450Mhz but each

input must not exceed the range 0v to +3.3V (of this

module). This means a 2.8V DC offset is required.

Zero input noise typically 3 levels maximum 10

levels

Offset typically +-8 levels maximum +-16 levels

- Analogue O/P

specifications

Standard Output

characteristics:

2 single ended channels with independent clocking

+/-0.374V single ended output on MMT co-axial

connector

A/C coupled 50R, signal B/W from 725Hz to 200Mhz

Optional Output types:

D/C 50R, signal B/W 0 ?200Mhz

Differential

+/-2.1V differential, on a pair of U.FL co-axial

connectors per channel

A/C coupled 50R, signal B/W from 750Hz to 145Mhz

D/C coupled 50R, signal B/W from DC to 145Mhz

|

|

|