| Quickly

explore design trade-offs |

|

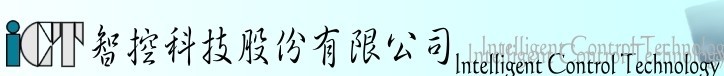

一旦把 MATLAB M-files

到

AccelChip 中,則 Design Flow Manager

工具會帶領你一步一步分析、轉換浮點和定點、整合、証實和最佳化。

在 AccelChip 中的

Project Navigator

工具,可以分析你所設計的 M-files,並以圖表的方式來表達設計階層,也確認設計裡的迴圈和決定設計的輸入和輸出。利用

Project Navigator 來做圖表瀏覽階層,來看

M-files

和 HDL 設計中的完整性。

透過使用者介面,你可以輕易的控制綜合的操作,像是DSP演算法中的串列和並列的比較,使設計團隊在晶片設計同時快速的選擇使用那一種。

你也可以發現在記憶體中儲存範圍的控制清單、使用資源和資料映射與速度做比較。

|

|

|

| From

floating- to fixed-point arithmetic |

|

典型的 DSP

設計者在MATLAB發展演算法,是利用浮點的計算技術。在

RTL

設計創立前,轉換定點計算技術也許是不存在的。

AccelChip可以快速的自動執行MATLAB中的變數由浮點轉成用定點代表。

自從AccelChip開始設計MATLAB浮點型式,就不需要把你的MATLAB

M-files再利用 Simulink

把演算法轉成定點運算了。

|

|

| Generate

optimized RTL model and simulation testbench |

|

從MATLAB中建立一個RTL模型是完成晶片的重要動作。

AccelChip 是可以建立專門的 FPGA

裝置的RTL模型。AccelChip的Resource

Description Language可以使從主要

FPGA 供應商, FPGAs

的實施的資源確保半導體裝置的有效使用。

檢驗演算法轉移到實體上是必要的,但是這不用花太多的時間。為了確保所完成的DSP設計能夠相容,AccelChip會自動的建立測試,使用MATLAB中的向量摸擬來演算你的RTL設計,移除不必要的程式。

|

|

| AccelWare—

Libraries of optimized DSP components |

|

AccelWare libraries內有許多有關DSP的方塊,由經驗充足的DSP設計者發展和最佳化。

AccelWare支援了許多高階 MATLAB

函數或是 Simulink

方塊的硬體連結。 AccelWare

方塊使用和標準的

MATLAB 工具箱和 Simulink

方塊的相同的參數。

增加額外的元件變數是需要精細的設計,像是計時器。所有

AccelWare IP 方塊都是建立於DSP設計的基礎上。

|

|

| Platform

Support |

| Microsoft Windows |

|

Unix

|

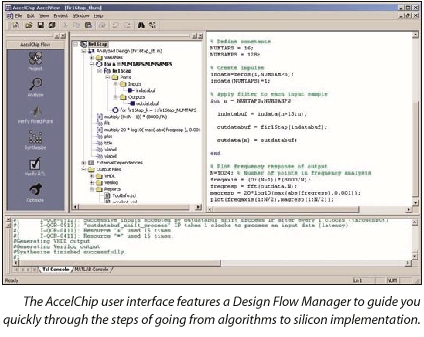

| AccelChip

Partners |

|

|

|